Copying and reproduction of contents and images in any form is prohibited. Furthermore, the redistribution and publication of contents and images not expressly authorized by the author or by the University of Modena and Reggio Emilia is prohibited

# Smart Systems for Data Acquisition Course Presentation

**UniMORE - LM Digital Automation Engineering**

Alessandro Bertacchini

Fabrizio Pancaldi

alessandro.bertacchini@unimore.it fabrizio.pancaldi@unimore.it

#### What is a Data Acquisition System?

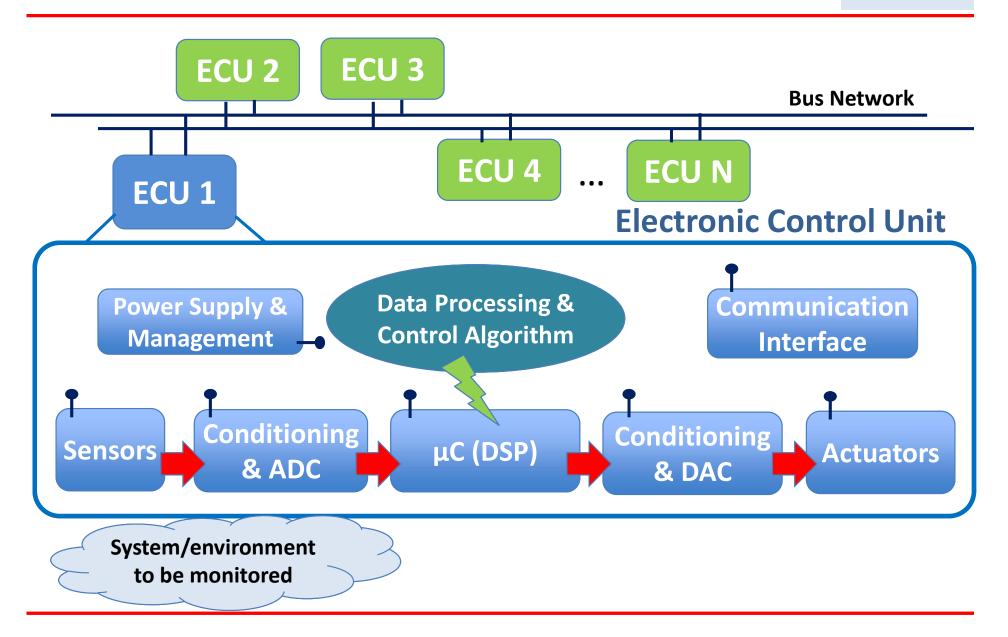

GENERAL Scenario

Smart Systems for Data Acquisition - LM Digital Automation Engineering – A. Bertacchini, F.Pancaldi - UniMORE

#### What is a Data Acquisition System?

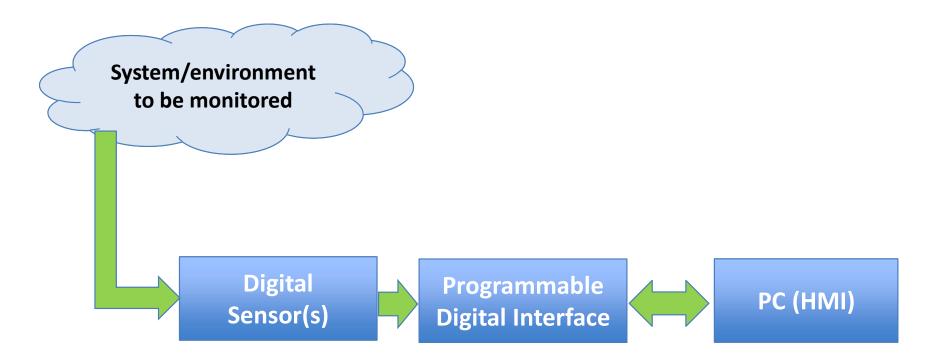

SIMPLIFIED

Scenario

## Goal & ToC

# GOAL: developing specific skills in the electronic design of data acquisition systems for real industrial applications

- 1. Sensors & Transducers: definitions, operation principles of the main sensors used in industrial applications, calibration

- 2. Analog-to-Digital converters (ADC): Fundamentals of A/D conversion, main topologies and operation principles

- 3. Sampling theorem and quantization On-Board and Board-to-Board communication protocols: UART, SPI, I2C, CAN

- 4. Discrete Fourier Transform

- 5. Finite impulse response (FIR) digital filters

- 6. Laboratory activities aiming to develop the exam project

#### • Prerequisites

- Circuit theory, Basic knowledge of programming

- Attitude to develop multidisciplinary projects

- Course teaching consists of

- lectures in the presence

- laboratory activities

#### • Teaching & Supporting Material

- slides, handouts, source codes, datasheets, etc... will be available on the Moodle's courses page

- Moodle is the only OFFICIAL REPOSITORY of the course

## **Practical Information**

- Student Reception:

- by appointment (via e-mail)

- at the end of the lectures

- Each communication must be

- Sent ONLY by using your account @studenti.unimore.it

- Addressed to both the teachers with the only exception of technical requests on a specific topic of the program

## The Exam

# • <u>PART 1</u>: Design and Implementation of a simple data acquisition system (0-30 points)

- Individual project proposed by the student inspired by a real application

- The proposed system must use at least one sensor with digital interface (e.g. UART/USART, SPI, I2C)

- The students must produce a **short report** containing the description of the system, the design choices taken and the description of the tests carried out to verify the proper operation of the prototype.

- Live Demo of the prototype on duty

- The project's grade will consider completeness of the report, project files and live demo to prove the proper operation of the prototype

#### PART2: Oral test

- 4 questions about the course's contents

- Each question will receive a score from 0 to 8 points

- The typical duration is 30 minutes

#### (0-32 points)

# **Final Grade**

- The overall grade is the **weighted average** of the grades obtained in the two PARTS

- PART 1- Project: 60%

- PART 2- Oral exam: 40%

- The final grade will be rounded to the nearest integer number

- The exam is passed if overall grade  $\geq 18/30$

- Honor if overall grade  $\geq 30/30$

#### **Practical Example**

- Project: 27/30

- Oral exam: 32/30

- Final grade: 27\*0.6 + 32\*0.4 = 29.60 rounded to 30/30

### **Exam Sessions**

- Technical discussion, live demo and oral examination will take place the same day

- Enrollment on www.esse3.unimore.it is MANDATORY and list closes ONE WEEK BEFORE the scheduled date

- Report and all the project's files must be sent to both the lecturers AT LEAST ONE WEEK BEFORE the chosen date

- Exam sessions in the scheduled dates ONLY (communicated through the normal channels)

- WINTER (Jan Feb): 3 dates (scheduled as soon as possible)

- 2<sup>nd</sup> SEMESTER BREAK: 1 date

- SUMMER (Jun Sept): 3 dates (to be defined)

- 1<sup>st</sup> SEMESTER BREAK 2024/25:1 date (to be defined)

### Timeline

| Semester | Semester |

|----------|----------|

| Start    | End      |

|                                                                                   | Bre                                                          | eak           |        |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------|---------------|--------|

| Course<br>Start                                                                   | Deadline for<br>project proposal<br>Projects<br>Presentation | Course<br>End | Buffer |

| Suggestion:<br>Take the opportunity to start the<br>development of your projects! |                                                              |               |        |